#### MESSAGE FROM THE HON'BLE CHANCELLOR

Dr. P.Shyama Raju Chancellor REVA University

REVA University has seen the light of the day to imbibe this character of paradigm shift in academic pursuits to contribute to the knowledge society. REVA works hard to bring in you an exciting and rewarding educational experience, to discover new interests and to develop your career prospects. You will benefit from a unique approach to student-centered learning through group work and individual study tackling real world challenges alongside experienced practitioners and researchers.

REVA has excellent learning facilities including custom built teaching facilities designed specifically to emulate working conditions, air-conditioned library opened for your studies from early morning till midnight and facilities for variety of sports and cultural activities.

Our faculties have introduced socially relevant and market driven engineering courses after studying the requirements of industries in detail and consulting entrepreneurs, experts in different areas of commerce and industry and other stake-holders. I am glad that the Choice Based Credit System (CBCS) and Continuous Assessment Grading Pattern (CAGP) being adopted will facilitate learning environment under continuous guidance and monitoring by the faculty and equip you with competent skills to opt for different job prospects across the global.

I hope that the present scheme of instructions, continuous periodic progress assessments, course curriculum of M.Tech in VLSI and Embedded Systems and other information provided in this hand book will guide you to choose appropriate courses of study and move ahead in the right direction in your chosen area of study. I hope you will enjoy and experience the curriculum, the student-centered teaching and learning ambience in developing your personality to become successful professionals, entrepreneurs and proud citizens of the country.

I wish you every success in your career.

#### MESSAGE FROM THE HON'BLE VICE-CHANCELLOR

Higher education across the globe is opening doors of its academic disciplines to the real world experiences. The disciplinary legitimacy is under critical review. Trans-border mobility and practice learning are being fore-grounded as guiding principles. Interactive learning, bridging disciplines and facilitating learners to gain different competencies through judicious management of time is viewed as one of the greatest and fascinating priorities and challenges today.

All the programs in REVA University are designed with a great care and after detailed market survey of present requirements and job opportunities. Experts in respective areas of study from primary institutions, industries, research organizations, business sectors and such others have been involved in designing the curriculum of each program.

The L: T: P structure of teaching and learning under Choice Based Credit System (CBCS) and Continuous Assessment Grading Pattern (CAGP) would certainly help our students learn and build competencies needed in this knowledge based society. It provides students an opportunity to choose subject(s) of interest in other areas of study and learn courses with students of different subjects. It facilitates cross cultural learning. It further facilitates students to move in fast track and earn additional certificates and diploma.

The well qualified, experienced, committed teachers in REVA University will involve students in integrative learning and application environment within and outside the university. They will certainly mould them with knowledge, skill and ethical values and empower them to face the competitive world with courage and confidence.

This handy document containing a brief information about M.Tech in VLSI and Embedded Systems, scheme of instruction, course content, CBCS-CAGP regulations and its advantages and calendar of events for the year will serve as a guiding path to students to move forward in a right direction. It is for the students to be disciplined, committed and to work hard and make use of enormous resources and expert faculties to accomplish all round development of their personalities and succeed with flying colours not only in earning degree but also in their future career as leaders and proud citizens of mother India.

Dr. V.G.Talawar Vice-Chancellor

#### MESSAGE FROM THE HON'BLE PRINCIPAL DIRECTOR

The curriculum of an institution of higher learning is a living entity. It evolves with time; it reflects the ever changing needs of the society and keeps pace with the growing talent of the students and the faculty. The curriculum of the B. Tech, M.Tech and other programs of REVA University is no exception.

An experience of a decade in preparing graduates and postgraduates in engineering, architecture, law, commerce and science for a wide variety of industries & research level organizations has led to creation of the new curriculum. I sincerely believe that it will meet the aspirations of all stake holders – students, faculty and the employers of the graduates and postgraduates of REVA University.

The curriculum has been designed in such a way that the teacher enjoys freedom to expand it in any direction he feels appropriate and incorporates the latest knowledge and stimulates the creative minds of the students. There is also provision for new experiments with new contents and new techniques. This is going to lead to new teaching — learning paradigm with experiential, experimental & industry relevant approaches. The present curriculum is contemporary because it is culmination of efforts of large number of faculty members, experts from industries and research level organizations. An effort of benchmarking this curriculum with curriculum of other institutions of repute like NITs and IITs has been done.

I am very sure that all students of REVA University enjoy this curriculum and take fullest advantage to expose themselves to fundamentals and applications. Also, imbibe all attributes that are required to term them as Global Engineers. The innovativeness and creativity being introduced should be explored fully by our students.

The flexibility in the curriculum permits staff and students to incorporate changes in terms of addition of new courses and deletion of irrelevant courses keeping the rapid advances in the technology into consideration.

I also record my personal gratitude to Chancellor, Vice chancellor and members of Academic Senate who have lent every bit of their wisdom to make this curriculum truly superior.

Dr. S.Y.Kulkarni Principal Director - Academics

#### **PREFACE**

The M. Tech in VLSI and Embedded System is designed keeping in view the current situation and possible future developments, both at national and international levels. This course is designed to give greater emphasis on VLSI and Embedded System design with a flexibility to explore any of the implementation platform and application field through a number of soft core courses providing knowledge in these specialized areas. This facilitates the students to choose specialized areas of their interest. Adequate attention is given to provide students the basic concepts and requisite skills.

The area of VLSI design has gained enormous popularity over the past few decades due to the rapid advancements in integrated circuit (IC) design and technology. The ability to produce miniaturized circuits with high performance in terms of power and speed is the reason for its popularity. Using ASIC technology, it has been possible to develop high performance multi-core processors. Verification and testing of such complex designs is a critical and challenging task to ensure the quality of the resulting circuits. The advances in EDA software and CAD tools alleviate the effort necessary to carry out the cumbersome design and verification process of ICs.

The program is designed to expose students to various courses having applications in VLSI and Embedded System like Digital VLSI design, ASIC design, SOC design, Low Power VLSI, High Speed VLSI design, VLSI Testing and verification, CMOS RF Circuit design, Low Power Embedded system. They are also exposed to basic concepts of NANO technology, VLSI testing and Verification, fabrication process, MEMS, Application specific design and embedded platform like ARM, MSP430, low power microcontrollers and FPGA, through outcome based teaching and learning process which emphasizes practical exposure rather than memorization. A variety of activities such as mini projects, seminars, internships, certification programs, etc. in consultation with industries will be carried out. There is also a scope for cultural, social and community service activities for the students to shape their personality suitable for all-round development.

The VLSI and Embedded System students can choose their career in any VLSI and Embedded System development industries. Now a days almost every appliance is coming with some VLSI component. The scope of VLSI and Embedded System is very wide covering almost every home appliances, industry, automotives, and medical appliance manufactures industry automation and control, telecommunication, Computer and Digital Systems, defense and space exploration.

I am sure the students choosing M Tech in VLSI and Embedded System in School of Electronics and Communication Engineering in REVA University will enjoy the curriculum, teaching and learning environment, the vast infrastructure and the experienced teachers involvement and guidance. We will strive to provide all needed comfort and congenial environment for their studies. I wish all students pleasant stay in REVA and grand success in their career.

Prof. Rajashekhar C. Biradar

Director

School of Electronics and Communication Engineering

# **CONTENTS**

| Sl. No. | Particulars                                                                                                                                                                                                                       | Page No. |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 01      | About School of Electronics and Communication Engineering - Vision - Mission - Values - Academic objectives - Members of Board of Studies - Advisory Board                                                                        | 8        |

| 02      | CBCS (Choice Based Credit System) and CAGP (Continuous Assessment and Grading Pattern) of education and its advantages                                                                                                            | 12       |

| 03      | Brief Outline of REVA University Regulations for Choice<br>Based Credit System (CBCS) and Continuous Assessment<br>Grading Pattern (CAGP) for Engineering degree Program                                                          | 12       |

| 04      | M. Tech in VLSI AND EMBEDDED SYSTEMS  - Eligibility  - Scheme of Instructions  - Description of Course  - Course Objective  - Course Contents  - Learning Outcomes  - Skill Development Activity  - Text books  - Reference books | 23       |

| 05      | Technical Skill Development                                                                                                                                                                                                       | 63       |

| 06      | Do's and Don'ts                                                                                                                                                                                                                   | 64       |

#### **RUKMINI EDUCATIONAL CHARITABLE TRUST**

It was the dream of late Smt. Rukmini Shyama Raju to impart education to millions of underprivileged children as she knew the importance of education in the contemporary society. The dream of Smt. Rukmini Shyama Raju came true with the establishment of Rukmini Educational Charitable Trust (RECT), in the year 2002. Rukmini Educational Charitable Trust (RECT) is a Public Charitable Trust, set up in 2002 with the objective of promoting, establishing and conducting academic activities in the fields of Arts, Commerce, Education, Engineering, Environmental Science, Management and Science & Technology, among others. In furtherance of these objectives, the Trust has set up the REVA Group of Educational Institutions comprising of REVA Institute of Technology & Management (RITM), REVA Institute of Science and Management (RISM), REVA Institute of Management Studies (RIMS), REVA Institute of Education (RIE), REVA First Grade College (RFGC), REVA Degree College (Evening), REVA Independent PU College at Kattigenahalli, Ganganagar and Sanjaynagar and now REVA University. Through these institutions, the Trust seeks to fulfill its vision of providing world class education and create abundant opportunities for the youth of this nation to excel in the areas of Engineering, Commerce, Management, Education, Arts and Science & Technology.

Every great human enterprise is powered by the vision of one or more extraordinary individuals and is sustained by the people who derive their motivation from the founders. The Chairman of the Trust is Dr. P. Shyama Raju, a developer and builder of repute, a captain of the industry in his own right and the Chairman and Managing Director of the DivyaSree Group of companies. The idea of creating these top notch educational institutions was born of the philanthropic instincts of Dr. P. Shyama Raju to do public good, quite in keeping with his support to other socially relevant charities such as maintaining the Richmond road park, building and donating a police station, gifting assets to organizations providing accident and trauma care, to name a few.

The Rukmini Educational Charitable Trust drives with the main aim to help students who are in pursuit of quality education for life. REVA is today a family of ten institutions providing education from PU to Post Graduation and Research leading to M. Phil and PhD degrees. REVA has well qualified experienced teaching faculty of whom majority are doctorates. The faculty is supported by committed administrative and technical staff. Over 9,000 students study various courses across REVA's three campuses equipped with exemplary state-of-the-art infrastructure and conductive environment for the knowledge driven community.

#### **ABOUT REVA UNIVERSITY**

REVA University established under the Government of Karnataka Act 80 of the year 2012 and notified in the Karnataka Gazette dated 7<sup>th</sup> Feb, 2013, is located 22 kms away from the Bangalore International Airport on the way to Bangalore city. The university has a sprawling lush green campus spread over 42 acres of land equipped with state-of-the-art infrastructure and conductive environment for higher learning.

The REVA campus has well equipped laboratories, custom-built teaching facilities designed specifically to emulate working conditions, fully air-conditioned library and central computer center kept open from morning 8.00 AM till mid-night for the students and the faculty. The well planned sports facility for variety of sports activities, facilities for cultural programs and friendly campus lifestyle add to the overall personality development of students. The campus also has residential facility for students, faculty and other staff.

Currently, REVA University offers 18 Post Graduate programs and 8 Graduate programs in Engineering and Technology, Science, Commerce and Management in addition to research degrees leading to PhD in different disciplines. The University aims to offer many more PG and UG programs in Science, Arts, Commerce, Engineering & Technology, Management Studies, Education, in the years to come.

The programs being offered by the REVA University are well planned and designed after detailed study with emphasis with knowledge assimilation, applications, global job market and their social relevance. Highly qualified, experienced faculty and scholars from reputed universities / institutions, experts from industries and business sectors have contributed in preparing the scheme of instruction and detailed curricula for this program. Greater emphasis on practice in respective areas and skill development to suit to respective job environment has been given while designing the curricula. The Choice Based Credit System and Continuous Assessment Graded Pattern (CBCS - CAGP) of education has been introduced in all programs to facilitate students to opt for subjects of their choice in addition to the core subjects of the study and prepare them with needed skills. The system also allows students to move forward under the fast track for those who have the capabilities to surpass others. These programs are taught by well experienced qualified faculty supported by the experts from industries, business sectors and such other organizations. REVA University has also initiated many supportive measures such as bridge courses, special coaching, remedial classes, etc., for slow learners so as to give them the needed input and build in them confidence and courage to move forward and accomplish success in their career. The University has also entered into MOUs with many industries, business firms and other institutions seeking their help in imparting quality education through practice, internship and also assisting students' placements.

#### ABOUT SCHOOL OF ELECTRONICS AND COMMUNICATION ENGINEERING

The School of Electronics and Communication Engineering headed by a highly experienced Professor and is supported by well qualified faculty members. The school has the state-of-art class rooms and well equipped laboratories. It offers B.Tech and M.Tech programs in various specialized streams. The school also has research program leading to doctoral degree. The curriculum of both graduate and post graduate degree programs have been designed to bridge the gap between industry – academia and hence they are industry application oriented. The B. Tech program aims to prepare human resources to play a leading role in the continuing adventure of modern automated systems and communications. The Master degree programs focus on research and design in the core and IT industries, building and marketing the next generation of product development. This is reflected in various core subjects offered within the program. B. Tech program offers numerous choices of study for the students based on interest in the current state of art technology. Apart from fundamental courses in Electronics and Communication Engineering, the school facilitates to study in four streams such as Circuits and Devices, Communication Engineering, Signal Processing and Programming. Students are at liberty to choose from these streams in higher semesters. However, there is no restriction of cross migration from one stream to another at any level and thus there is a flexibility provided in the course duration.

The faculty members have number of publications in reputed national and international journals/conferences. The school is also involved in funded research projects. The other important features of the school are individual counseling of students for academic performance, additional coaching classes for important subjects for all the semesters, soft skill development classes, scientific and student centered teaching-learning process.

Student's welfare is given utmost priority here at School of Electronics and Communication Engineering. Advanced learning methods are adopted to make learning truly interactive. More focus is on discussion and practical applications rather than rote learning. Notes/handouts are given and critical thinking questions are asked to test understanding. Experienced, well qualified and friendly faculty members always strive hard to provide best of education to students.

#### Vision

The School of Electronics and Communication Engineering is envisioned to be a leading centre of higher learning with academic excellence in the field of electronics and communication engineering blended by research and innovation in tune with changing technological and cultural challenges.

#### Mission

• Establish a unique learning environment to enable the students to face the challenges of the Electronics and Communication Engineering field.

- Promote the establishment of centers of excellence in niche technology areas to nurture the spirit of innovation and creativity among faculty and students.

- Provide ethical and value based education by promoting activities addressing the societal needs.

- Enable students to develop skills to solve complex technological problems of current times and also provide a framework for promoting collaborative and multidisciplinary activities.

# **Program Educational Objectives (PEO's)**

The programme educational objectives of the Electronics and Communication Engineering of REVA University is to prepare graduates

| PEO-1 | To have successful professional careers in national and multinational organization and   |  |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | communicate effectively as a member of a team or to lead a team.                         |  |  |  |  |  |  |  |

| PEO-2 | To continue to learn and advance their careers through activities such as research and   |  |  |  |  |  |  |  |

|       | development, acquiring doctoral degree, participation in national level research         |  |  |  |  |  |  |  |

|       | programmes, teaching and research at university level etc.,                              |  |  |  |  |  |  |  |

| PEO-3 | To be active members ready to serve the society locally and internationally, may take up |  |  |  |  |  |  |  |

|       | entrepreneurship for the growth of economy and to generate employment; and adopt the     |  |  |  |  |  |  |  |

|       | philosophy of lifelong learning to be aligned with economic and technological            |  |  |  |  |  |  |  |

|       | development.                                                                             |  |  |  |  |  |  |  |

# **Program Outcomes (POs)**

# After successful completion of the programme, the graduates shall be able to

- PO1. **Demonstrate in-depth knowledge** of VLSI and Embedded Systems, including wider and global perspective, with an ability to discriminate, evaluate, analyze and synthesize existing and new knowledge, and integration of the same for enhancement of knowledge.

- PO2. **Analyze complex engineering problems critically**, apply independent judgment for synthesizing information to make intellectual and/or creative advances for conducting research in a wider theoretical, practical and policy context.

- PO3. Think laterally and originally, conceptualize and solve engineering problems, evaluate a wide range of potential solutions for those problems and arrive at feasible, optimal solutions after considering public health and safety, cultural, societal and environmental factors in the core areas of expertise.

- PO4. Extract information pertinent to unfamiliar problems through literature survey and experiments, apply appropriate research methodologies, techniques and tools, design, conduct experiments, analyze and interpret data, demonstrate higher order skill and view things in a broader perspective, contribute individually/in group(s) to the development of scientific/technological knowledge in one or more domains of engineering.

- PO5. **Create, select, learn and apply appropriate techniques**, resources, and modern engineering and IT tools, including prediction and modeling, to complex engineering activities with an understanding of the limitations.

- PO6. Possess knowledge and understanding of group dynamics, recognize opportunities and contribute positively to collaborative-multidisciplinary scientific research, demonstrate a capacity for self-management and teamwork, decision-making based on open-mindedness, objectivity and rational analysis in order to achieve common goals and further the learning of themselves as well as others.

- PO7. **Demonstrate knowledge and understanding** of engineering and management principles and apply the same to one's own work, as a member and leader in a team, manage projects efficiently in respective disciplines and multidisciplinary environments after consideration of economical and financial factors.

PO8. Communicate with the engineering community, and with society at large, regarding complex engineering activities confidently and effectively, such as, being able to comprehend and write effective reports and design documentation by adhering to appropriate standards, make effective presentations, and give and receive clear instructions.

PO9: **Recognize the need for**, and have the preparation and ability to engage in **life-long learning** independently, with a high level of enthusiasm and commitment to improve knowledge and competence continuously.

PO10. **Acquire professional and intellectual integrity,** professional code of conduct, ethics of research and scholarship, consideration of the impact of research outcomes on professional practices and an understanding of responsibility to contribute to the community for sustainable development of society.

PO11. **Observe and examine critically the outcomes** of one's actions and make corrective measures subsequently, and learn from mistakes without depending on external feedback (**SELF learning**)

# **Programme Specific Outcomes (PSO's)**

#### After successful completion of the programme, the graduates shall be able to

- Isolate and solve complex problems in the domains of VLSI and Embedded Systems

using latest hardware and software tools and technologies, along with analytical and

managerial skills to arrive at cost effective and optimum solutions either independently

or as a team.

- Implant the capacity to apply the concepts of FPGA, ASIC, System On Chip, IoT and cyber physical systems, etc. in the design, development and implementation of application oriented engineering systems

- 3. Design, Model, Analyze and VLSI and Embedded Systems to solve real life and industry problems.

# **Board of Studies for School of Electronics and Communication Engineering**

| SI.<br>No. | Name, Designation & Affiliation                                            | Status               |

|------------|----------------------------------------------------------------------------|----------------------|

| 1          | Dr. R. C. Biradar Director, School of ECE, Reva University, Bangalore      | Chair Person         |

| 2          | Dr. Rathna G. N. Principal Research Scientist, E&E Dept., IISc., Bangalore | Member               |

| 3          | Dr.Vasantha M. H. HOD, Dept. of ECE, NIT,Goa                               | Member               |

| 4          | <b>Dr. VaibhavMeshram</b> Director, Jain University, Bangalore             | Member               |

| 5          | Mr. Chandra Mohan<br>CEO, Goshakthi Renewable, Bangalore                   | Member               |

| 6          | Dr. K. S. Gurumurthy Senior Professor, School of ECE, Reva University      | Member<br>(Internal) |

| 7          | <b>Dr. Venkata Siva Reddy</b> Professor, School of ECE, Reva University    | Member<br>(Internal) |

| 8          | <b>Dr. Bharathi S. H.</b> Professor, School of ECE, Reva University        | Member<br>(Internal) |

| 9          | Prof.Jayaraman K. Adjunct Professor, School of ECE,Reva University         | Member<br>(Internal) |

| 10         | <b>Dr. Geetha D. D.</b> Professor, School of ECE, Reva University          | Member<br>(Internal) |

| 11         | Dr. P. I. Basarkod Professor, School of ECE, Reva University               | Member<br>(Internal) |

# **Advisory Board for School of Electronics and Communication Engineering**

| Sl.No | Name and affiliation                                                |

|-------|---------------------------------------------------------------------|

| 1     | Dr. M.H.Kori,                                                       |

|       | Technology Consultant, Technology Adviser Validus Technologies USA, |

|       | Retd. Technical Director, Alcatel-Lucent Technologies, Bangalore    |

| 2     | Dr. Vinod Sharma                                                    |

|       | Professor, ECE Department, IISc. Bangalore                          |

| 3     | Dr. Surendra Pal                                                    |

|       | Former ISRO Scientist, President, IETE-India, Bangalore             |

| 4     | Dr. Shirshu Varma                                                   |

|       | Professor, Department of Computer Science and Engineering           |

|       | IIIT Allahabad                                                      |

| 5     | Dr. Rathna                                                          |

|       | Principal Research Scientist, Department of Electrical Engineering  |

|       | IISc., Bangalore                                                    |

| 6     | Dr. ArzadAlamKherani                                                |

|       | Samsung R and D, Bangalore                                          |

| 7     | Dr. MahadevPrasanna                                                 |

|       | Department of Electrical and Electronics Engineering                |

|       | IIT Guwahathi                                                       |

| 8     | Dr. Muralidhara Kulkarni                                            |

|       | Department of Electronics & Communication Engineering,              |

|       | NITK, Surathkal                                                     |

| 9     | Dr. Kumarashama                                                     |

|       | Department of Electronics & Communication Engineering,              |

| 10    | Manipal Institute of Technology, Manipal                            |

| 10    | Dr.Vijayaprakash                                                    |

|       | Department of Electronics & Communication Engineering,              |

|       | Bangalore Institute of Technology, Bangalore                        |

| 11    | Mr.Aravinda Sharma,<br>Manager,Delphi Systems, Bangalore            |

| 12    | Dr. Kashinath, Director, ALS Semiconductors, Bangalore              |

| 13    | Mr.LokeshaRai K, Director, Symphony Telecca Services, Bangalore     |

| 14    | Mrs.Deepa, Senior Engineer, Intel Corporation, Bangalore            |

| 14    | iviis.Deepa, seilioi Eligilieet, ilitei Corporation, bangaiore      |

# CBCS (CHOICE BASED CREDIT SYSTEM) AND CAGP (CONTINUOUS ASSESSMENT AND GRADING PATTERN) OF EDUCATION AND ITS ADVANTAGES

CBCS is a proven, advanced mode of learning in higher education. It facilitates students to have freedom in making their own choices for acquiring a Degree / Masters Degree program. It is more focused towards the student's choice in providing a wide range of modules available in a single campus across various disciplines offered by experts in the subjects. It leads to quality education with active teacher-student participation.

# **Studying under CBCS has following advantages:**

- Students may undergo training in cross-disciplinary and multi-disciplinary subjects and acquire more focused and preferred knowledge.

- Students may get more skills from other subject(s) which are required for the career path in addition to their regular subject knowledge.

- Students may get ample opportunities to use the laboratories and gain practical exposure to the much needed modules available in other departments/schools for want of scientific inputs.

- Courses are conducted by subject experts identified on the basis of their experiences.

Courses taught by such experts may provide in-depth information and clear understanding of the modules.

- Students may get an opportunity to study courses with other students of different programs and exchange their views and knowledge in a common class room.

- CBCS provides a cross-cultural learning environment.

- Students may benefit much from selecting the right options to successfully face the public service examinations like UPSC, KPSC, IFS, IES wherein the knowledge of additional subjects become mandatory for general or optional papers.

- Students are exposed to the culture of universal brotherhood during their campus life.

- Students are allowed to practice various methods of learning a subject.

# Brief Summary of REVA University Regulations for Choice Based Credit System (CBCS) and Continuous Assessment Grading Pattern (CAGP) for Engineering Degree Program

#### 1.0 Teaching and Learning Process

The teaching and learning process under CBCS-CAGP of education in each course of study will have three components, namely,

(i) L= Lecture (ii) T= Tutorial (iii) P= Practice, where:

**L** stands for **Lecture** session consisting of classroom instruction.

T stands for Tutorial session consisting participatory discussion / self-study/ desk work/ brief seminar presentations by students and such other novel methods that make a student to absorb and assimilate more effectively the contents delivered in the Lecture classes.

**P** stands for **Practice** session and it consists of Hands on Experience / Laboratory Experiments / Field Studies / Case Studies that equip students to acquire the much required skill component.

#### 2.0 Course of Study and Duration:

The study of B Tech degree is grouped under various courses. Each of these course carries credits which are based on the number of hours of teaching and learning. In the teaching-learning process every **one hour session of L amounts to 1 credit per Semester.** In case of **T or P** minimum of **two hour session amounts to 1 credit or a three hour session amounts to 2 credits per semester of 16 weeks.**

The total duration of a semester is 20 weeks inclusive of semester-end examination.

A course shall have either or all the three components. That means a course may have only lecture component, or only practical component or combination of any two or all the three components.

- **2.1.** Various course of study are labeled and defined as: (i) Core Course (CC), (ii) Hard Core Course (HC), (iii) Soft Core Course (SC), (iv) Foundation Core Course (FC) and (v) Open Elective Course (OE).

- (i) **Core Course:** A course which should compulsorily be studied by a candidate as a core-requirement is termed as a Core course.

- (ii) Foundation Course (FC):

- The foundation Course is a core course which should be completed successfully as a part of graduate degree program irrespective of the branch of study.

- (iii) Hard Core Course (HC):

The Hard Core Course is a Core Course in the main branch of study and related branch(es) of study, if any that the candidates have to complete compulsorily.

- (iv) Soft Core Course (SC):

- A Core course may be a **Soft Core** if there is a choice or an option for the candidate to choose a course from a pool of courses from the main branch of study or from a sister/related branch of study which supports the main branch of study.

- (v) Open Elective Course:

- An elective course chosen generally from other discipline / subject, with an intention to seek exposure is called an **Open Elective Course**.

#### 2.2. Project Work:

Project work is a special course involving application of knowledge in solving / analyzing /exploring a real life situation / difficult problem.

#### 2.3. Minor Project:

A project work up to **FOUR to SIX** credits is called **Minor Project** work. A Minor Project work may be a hard core or a Soft Core as decided by the BoS / concerned.

#### 2.4. Major Project / Dissertation:

A project work of **EIGHT, TEN, TWELVE or SIXTEEN** credits is called **Major Project** work. The Major Project / Dissertation shall be Hard Core.

#### 3.0. Minimum Credits to be Earned:

- **3.1.** A candidate has to earn 192 credits for successful completion of B Tech degree with a distribution of credits for different courses as prescribed by the university.

- **3.2.** A candidate can enroll for a maximum of 32 credits per Semester. However he / she may not successfully earn a maximum of 32 credits per semester. This maximum of 32 credits does not include the credits of courses carried forward by a candidate.

- 3.3. Only such full time candidates who register for a minimum prescribed number of credits in each semester from I semester to VIII semester and complete successfully 192 credits in 8 successive semesters shall be considered for declaration of Ranks, Medals, Prizes and are eligible to apply for Student Fellowship, Scholarship, Free ships, and such other rewards / advantages which could be applicable for all full time students and for hostel facilities.

#### 4.0. Add- on Proficiency Certification:

In excess to the minimum of 192 credits for the B. Tech Degree program, a candidate can opt to complete a minimum of 4 extra credits either in the same discipline/subject or in different discipline / subject to acquire **Add on Proficiency Certification** in that particular discipline / subject along with the B. Tech. degree.

# 4.1. Add on Proficiency Diploma:

In excess to the minimum of 192 credits for the B. Tech degree program, a candidate can opt to complete a minimum of 18 extra credits either in the same discipline/subject or in different discipline / subject to acquire Add on Proficiency Diploma in that particular discipline / subject along with the B. Tech degree. The **add-on proficiency certification / diploma** so issued to the candidate contains the courses studied and grades earned.

# 5.0. Continuous Assessment, Earning of Credits and Award of Grades.

**5.1.** The assessment and evaluation process happen in a continuous mode. However, for reporting purpose, a semester is divided into 3 components as C1, C2, and C3.

The performance of a candidate in a course will be assessed for a maximum of 100 marks as explained below.

### (i) Component C1:

The first Component (C1), of assessment is for 25 marks. This will be based on test, assignment / seminar. During the first half of the semester (i.e. by 8th week), the first 50% of the syllabus (Unit 1&2) will be completed. This shall be consolidated during the first three days of 8th week of the semester. A review test based on C1 will be conducted and completed in the beginning of the 9th week. In case of courses where test cannot be conducted, the form of assessment will be decided by the concerned school and such formalities of assessment will be completed in the beginning of the 9th week. The academic sessions will continue for C2 immediately after completion of

# process of C1.

### (ii) Component C2:

The second component (C2), of assessment is for 25 marks. This will be based on test, assignment /seminar. The continuous assessment and scores of second half of the semester (9th to 16th week) will be consolidated during 16th week of the semester. During the second half of the semester the remaining units in the course will be completed. A review test based on C2 will be conducted and completed during 16th week of the semester. In case of courses where test cannot be conducted, the form of assessment will be decided by the concerned school and such formalities of assessment will be completed during 16th week.

The 17th week will be for revision of syllabus and preparation for the semester - end examination.

#### (iii) Component C3:

The end semester examination of 3 hours duration for each course shall be conducted during the 18th & 19th week. This forms the third / final component of assessment (C3) and the maximum marks for the final component will be 50.

# 5.2. Evaluation of Minor Project / Major Project / Dissertation:

Right from the initial stage of defining the problem, the candidate has to submit the progress reports periodically and also present his/her progress in the form of seminars in addition to the regular discussion with the supervisor. At the end of the semester, the candidate has to submit final report of the project / dissertation, as the case may be, for final evaluation. The components of evaluation are as follows:

| Component – I  | (C1) | Periodic Progress and Progress Reports (25%)            |

|----------------|------|---------------------------------------------------------|

| Component – II | (C2) | Results of Work and Draft Report (25%)                  |

| Component- III | (C3) | Final Evaluation and Viva-Voce (50%). Evaluation of the |

|                |      | report is for 30% and the Viva-Voce examination is for  |

# **5.3.** The details of continuous assessment are summarized in the following table:

| Component | Period                                                          | Syllabus                                | Weightage | Activity                                              |

|-----------|-----------------------------------------------------------------|-----------------------------------------|-----------|-------------------------------------------------------|

| C1        | 1st Week to<br>8 <sup>th</sup> Week                             |                                         |           | Instructional process<br>and Continuous<br>Assessment |

|           | Last 3 days of<br>8 <sup>th</sup> Week                          | First 50%<br>(two units)                | 25%       | Consolidation of C1                                   |

| 63        | From first day<br>of 9th Week<br>to first 3 days<br>of16th Week |                                         |           | Instructional process and Continuous Assessment       |

| C2        | Last 3 days of<br>16th Week                                     | Second<br>50%<br>remaining<br>two units | 25%       | Consolidation of C2                                   |

|           | 17th Week                                                       |                                         |           | Revision and preparation for Semester–end exam(C3)    |

| C3        | 18 <sup>th</sup> Week to<br>19th Week                           | Entire<br>syllabus                      | 50%       | Conduct of Semester-<br>end Exams (C3)                |

|           | 20 <sup>th</sup> Week                                           |                                         |           | Evaluation and<br>Tabulation                          |

|           | End of 20 <sup>th</sup><br>Week                                 |                                         |           | Notification of Final<br>Grades                       |

Note: Practical examination wherever applicable shall be conducted before conduct of C2 Examination. The calendar of practical examination shall be decided by the respective school.

A candidate's performance from all 3 components will be in terms of scores, and the sum of all three scores will be for a maximum of 100 marks (25 + 25 + 50).

# **5.4.** Provision for Make- up Examination:

For those students who have secured less than 40% marks in end semester examination (C3) the university shall conduct a make-up examination after the end of every semester and before the commencement of next subsequent semester.

Such of those students who have secured more than 30% marks in C1 and C2 together and less than 40% marks in the End Semester Examination (C3) in a given course shall appear for make-up examination in that course.

A student who is absent to End Semester Examination (C3) due to medical emergencies or such other exigencies and fulfills the minimum attendance and performance requirements in C1 & C2 shall appear for make-up examination.

#### 6.0. Re-Registration and Re-Admission:

In case a candidate fails in more than 4 courses in odd and even semesters together in a given academic year has to seek re-admission to those semesters during subsequent year within a stipulated period.

In case a candidate's class attendance in aggregate of all courses in a semester is less than 75% or as stipulated by the University, such a candidate is not allowed to appear for end semester examination (C3) and he / she shall have to seek re-admission to that semester during subsequent year within a stipulated period.

**6.1.** In such case a candidate drops all the courses in semester due to personal reasons he / she can take re-admission to such dropped semester.

# 6.2 Provision to carry forward the failed subjects / courses:

The student who has failed in 4 courses in odd and even semesters together shall move to next semester of immediate succeeding year of study. And he / she shall appear for C3 examination of failed courses of previous semesters concurrently with odd and even end semester examinations (C3) of current year of study. However, he / she shall have to clear all courses of both odd and even semesters of preceding year to register for next succeeding semester.

#### Examples:-

- 1) Student "A" has failed in one course in first semester and 3 courses in second semester. He / she is eligible to seek admission for third semester and appear for C3 examination of one failed course of first semester concurrently with third semester C3 examination. Likewise, he / she is eligible to appear for C3 examination of 3 failed courses of second semester concurrently with fourth semester C3 examination. However, he / she has to clear all the failed courses of first and second semesters before seeking admission to fifth semester.

- 2) Student "B" has failed in two courses in third semester and two courses in fourth semester and has passed in all courses of first and second semesters. He / she is eligible to seek admission to fifth semester and appear for C3 examination of two failed courses of third semester concurrently with fifth semester C3 examination. Likewise he / she is eligible to appear for C3 examination of two failed courses of fourth semester concurrently with sixth semester C3 examination. However, he / she is not eligible to seek admission to seventh semester unless he / she passes in all the failed courses of third and fourth semesters.

- 3) Student "C" has failed in four courses in first semester but has cleared all the courses in second semester. He / she is eligible to seek admission for third semester and appear for C3 examination of four failed courses of first semester concurrently with third semester C3

examination. However, he / she is not eligible to seek admission for fifth semester unless he / she clears all the four failed courses of first semester.

# 7.0. Attendance Requirement:

- a) All students must attend every lecture, tutorial and practical classes.

- b) In case a student is on approved leave of absence (e g:- representing the university in sports, games or athletics, placement activities, NCC, NSS activities and such others) and / or any other such contingencies like medical emergencies, the attendance requirement shall be minimum of 75% of the classes attended.

- c) Any student with less than 75% of attendance in a course in aggregate during a semester shall not be permitted to appear to the end semester (C3) examination.

- d) Teachers offering the courses will place the above details in the School / Department meeting during the last week of the semester, before the commencement of C3, and subsequently a notification pertaining to the above will be brought out by the Head of the School before the commencement of C3 examination. A copy of this notification shall also be sent to the office of the Registrar & Registrar (Evaluation).

# 7.1. Absence during mid-semester examination:

In case a student has been absent from a mid-semester examination due to the illness or other contingencies he / she may give a request along with necessary supporting documents and certification from the concerned class teacher / authorized personnel to the concerned Head of the School, for make-up examination. The Head of the School may consider such request depending on the merit of the case and after consultation with course instructor and class teacher, and permit such student to appear for make-up mid semester examination.

#### 7.2. Absence during end semester examination:

In case a student is absent for end semester examination on medical grounds or such other exigencies, the student can submit request for make-up examination, with necessary supporting documents and certification from the concerned class teacher / authorized personnel to the concerned Director of the School. The Director of the School may consider such request depending on the merit of the case and after consultation with class teacher, course instructor and permit such student to appear for make-up mid semester examination

#### 8.0. Challenge Valuation

A student who desires to apply for challenge valuation shall obtain a photo copy of the answer script by paying the prescribed fee within 10 days after the announcement of the results. He / She can challenge the grade awarded to him/her by surrendering the grade card and by submitting an application along with the prescribed fee to the Registrar (Evaluation) within 07days after the announcement of the results. This challenge valuation is only for C3 component.

The answer scripts for which challenge valuation is sought for shall be evaluated by

the external examiner who has not involved in the first evaluation. The higher of two marks from first valuation and challenge valuation shall be the final.

9.0. Provisional Grade Card: The tentative / provisional grade card shall be issued by the Registrar (Evaluation) at the end of every semester indicating the courses completed successfully. The provisional grade card provides Semester Grade Point Average (SGPA). The SGPA is the ratio of sum of the product of the number of credits with the grade points scored by a student in all the courses taken by a student and the sum of the number of credits of all the courses undergone by a student, i.e.

SGPA (Si) =

$$\sum$$

(Ci x Gi) /  $\sum$ Ci

Where Ci is the number of credits of the i<sup>th</sup> course and Gi is the grade point scored by the student in the i<sup>th</sup> course.

- **9.1. Final Grade Card:** Upon successful completion of B Tech Degree a Final Grade card consisting of Grades of all courses successfully completed by the candidate will be issued by the Registrar (Evaluation).

- **9.2.** The Grade and the Grade Point: The Grade and the Grade Point earned by the candidate in the subject will be as given below.

| Marks<br>P | Grade<br>G | Grade Point<br>(GP=V x G) | Letter<br>Grade |

|------------|------------|---------------------------|-----------------|

| 90-100     | 10         | v*10                      | 0               |

| 80-89      | 9          | v*9                       | Α               |

| 70-79      | 8          | v*8                       | В               |

| 60-69      | 7          | v*7                       | С               |

| 50-59      | 6          | v*6                       | D               |

| 40-49      | 5          | v*5                       | E               |

| 0-39       | 0          | v*0                       | F               |

O - Outstanding; A-Excellent; B-Very Good; C-Good; D-Fair; E-Satisfactory; F - Fail;

Here, P is the percentage of marks (P= [(C1+C2) +M] secured by a candidate in a course which is **rounded to nearest integer**. V is the credit value of course. G is the grade and GP is the grade point.

#### 9.3. Cumulative Grade Point Average (CGPA):

Overall Cumulative Grade Point Average (CGPA) of a candidate after successful completion of the required number of credits (192) for B. Tech degree in Engineering & Technology is calculated taking into account all the courses undergone by a student over

all the semesters of a program, i.e. : **CGPA = \sum (Ci x Si) / \sumCi** Where Si is the SGPA of the i<sup>th</sup> semester and Ci is the total number of credits in that semester.

The SGPA and CGPA shall be rounded off to 2 decimal points and reported in the transcripts.

#### **CONVERSION OF GRADES INTO PERCENTAGE:**

Conversion formula for the conversion of CGPA into Percentage is:

Percentage of marks scored = CGPA Earned x 10

Illustration: CGPA Earned 8.10 x 10 = 81.0

#### 10.0 Classification of Results

The final grade point (FGP) to be awarded to the student is based on CGPA secured by the candidate and is given as follows.

|                |                    | FGP                  |

|----------------|--------------------|----------------------|

| CGPA           | Numerical<br>Index | Qualitative<br>Index |

| > 4 CGPA < 5   | 5                  | CECOND CLASS         |

| 5 > = CGPA < 6 | 6                  | SECOND CLASS         |

| 6 >= CGPA < 7  | 7                  | FIDCT CLACC          |

| 7 >= CGPA < 8  | 8                  | FIRST CLASS          |

| 8 >= CGPA < 9  | 9                  | DISTINCTION          |

| 9 >= CGPA 10   | 10                 | DISTINCTION          |

# Overall percentage=10\*CGPA

### 11.0. Provision for Appeal

If a candidate is not satisfied with the evaluation of C1 and C2 components, he/she can approach the grievance cell with the written submission together with all facts, the assignments, and test papers etc., which were evaluated. He/she can do so before the commencement of semester-end examination. The grievance cell is empowered to revise the marks if the case is genuine and is also empowered to levy penalty as prescribed by the university on the candidate if his/her submission is found to be baseless and unduly motivated. This cell may recommend taking disciplinary/corrective action on an evaluator if he/she is found guilty. The decision taken by the grievance cell is final.

## 11.1. Grievance Cell:

For every program there will be one grievance cell. The composition of the grievance cell is as follows.

- The Registrar (Evaluation) Ex-officio Chairman / Convener

- One Senior Faculty Member (other than those concerned with the evaluation of the course concerned) drawn from the school / department/discipline and/or from the sister schools / departments/sister disciplines Member.

- One Senior Faculty Members / Subject Experts drawn from outside the University school / department Member.

- **11.2.** With regard to any specific case of ambiguity and unsolved problem, the decision of the Vice-Chancellor shall be final.

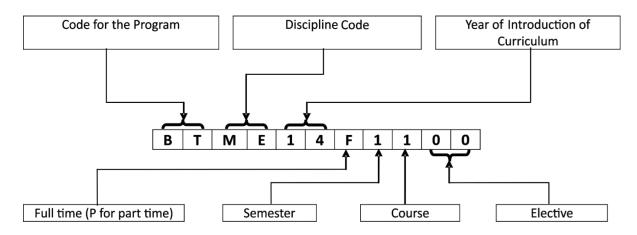

# **Course Numbering Scheme**

List of Codes for Programs and Disciplines / Branch of Study

| Program | Title of the Program                       | Discipline | Name of the Discipline / Branch of           |

|---------|--------------------------------------------|------------|----------------------------------------------|

| Code    |                                            | Code       | Study                                        |

| ВА      | Bachelor of Arts                           | AE         | Advanced Embedded Systems                    |

| ВВ      | BBM (Bachelor of Business<br>Management)   | AI         | Advanced Information Technology              |

| ВС      | B.Com (Bachelor of Commerce)               | AP         | Advanced Power Electronics                   |

| BR      | B. Arch (Bachelor of Architecture)         | CA         | Computer Aided Structural Engineering        |

| BS      | B Sc, BS (Bachelor of Science)             | CE         | Civil Engineering                            |

| BT      | B.Tech (Bachelor of Technology)            | СН         | Chemistry                                    |

| ВР      | Bachelor of Computer Applications          | СО         | Commerce                                     |

| BL      | LLB (Bachelor of Law)                      | CS         | Computer Science and Engineering /           |

| MA      | Master of Arts                             | DE         | Data Engineering and Cloud Computing         |

| MB      | MBA (Master of Business<br>Administration) | EC         | Electronics and Communication<br>Engineering |

| MC      | M.Com (Master of Commerce)                 | EN         | English                                      |

| MS      | M.Sc / MS (Master of Science)              | MD         | Machine Design and Dynamics                  |

| MT      | M Tech (Master of Technology)              | ME         | Mechanical Engineering                       |

| MC      | Master of Computer Applications            | EE         | Electrical & Electronics Engineering         |

# M. Tech. (VLSI and Embedded Systems) FULL-TIME

**Eligibility:** B.E./B. Tech. in ECE/TE/EEE/CSE/ISE/ Instrumentation Technology/ Medical Electronics/ Electrical and Electronics Engineering/ M Sc in Electronics with a minimum of 45% (40% in case of candidates belonging to SC and ST) marks in aggregate of any recognized university/institution or any other qualification recognized as equivalent there to.

# Scheme of Instruction 2016-17

| SI | Course Code | ourse Code Title of the Course Co    |    |   | Credi | t Patt | ern   | No. |

|----|-------------|--------------------------------------|----|---|-------|--------|-------|-----|

| No | Course Code | Title of the Course                  | SC | L | Т     | Р      | Total | Hrs |

|    |             | FIRST SEMESTER                       | ₹  |   |       |        |       |     |

| 1  | MTVS15F1100 | Advanced Mathematics                 | HC | 4 | 1     | 0      | 5     | 6   |

| 2  | MTVS15F1200 | Digital VLSI Design                  | НС | 4 | 0     | 1      | 5     | 6   |

| 3  | MTVS15F1300 | Digital System Design                | HC | 4 | 0     | 1      | 5     | 6   |

| 4  | MTVS15F1410 | Embedded System Design               | SC | 4 | 1     | 0      | 5     | 6   |

|    | MTVS15F1420 | Semiconductor Fabrication Technology |    |   |       |        |       |     |

| 5  | MTVS15F1510 | ASIC Design                          | SC | 4 | 1     | 0      | 5     | 6   |

|    | MTVS15F1520 | VLSI SOC Design                      |    | 4 | 1     | 0      |       |     |

|    |             | Total Credits                        |    |   |       |        | 25    | 30  |

|    |             | SECOND SEMESTE                       | :K |   |       |        |       |     |

| 6  | MTVS15F2100 | Design of CMOS VLSI Circuits         | HC | 4 | 0     | 1      | 5     | 6   |

| 7  | MTVS15F2200 | Real Time Systems                    | HC | 4 | 0     | 1      | 5     | 6   |

| 8  | MTVS15F2310 | Low Power VLSI Design                | SC | 4 | 1     | 0      | 5     | 6   |

|    | MTVS15F2320 | VLSI for Signal Processing           |    | 4 | 1     | 0      |       |     |

|    | MTVS15F2410 | High Speed VLSI Design               | SC | 4 | 1     | 0      | 5     |     |

| 9  | MTVS15F2420 | VLSI Testing and Verification        |    | 4 | 1     | 0      |       | 6   |

| 10 | MTVS15F2510 | MEMS and Nano-<br>Electronics        | SC | 4 | 1     | 0      | 5     |     |

|    | MTVS15F2520 | Advanced Computer<br>Architecture    |    | 4 | 1     | 0      |       | 6   |

|    |             | Total Credits                        |    |   |       |        | 25    | 30  |

| SI<br>No | Course Code          | HC/S                                 |    | ( | Credit | Patte | ern   | No.<br>Hrs |

|----------|----------------------|--------------------------------------|----|---|--------|-------|-------|------------|

|          |                      | Title of the Course                  |    | L | Т      | Р     | Total |            |

|          |                      | THIRD SEMESTEI                       | R  |   |        |       |       |            |

|          |                      | ,                                    |    |   | ı      | 1     | 1     | ,          |

| 11       | MTVS15F3110          | MSP430                               | SC | 4 | 0      | 1     | 5     | 6          |

|          | MTVS15F3120          | FPGA Based Embedded<br>System Design |    | 4 | 1      | 0     |       |            |

|          | MTVS15F3130          | Advanced Digital System Design       |    | 4 | 1      | 0     |       |            |

|          | MTVS15F3140          | CMOS RF Circuit Design               |    | 4 | 1      | 0     |       |            |

|          | MTVS15F3150          | Advances in VLSI Design              |    | 4 | 1      | 0     |       |            |

| 12       | MTVS15F3200          | Seminar/Certification Program        | НС | 4 | 1      | 0     | 5     | 6          |

| 13       | MTVS15F3300          | Internship/Mini Project              | НС | 0 | 2      | 8     | 10    | 22         |

| 14       | MTVS15F3400          | Automotive Electronics Systems       | OE | 3 | 1      | 0     | 04    |            |

|          |                      | Total Credits                        |    |   |        |       | 24    | 38         |

|          | FOURTH SEMESTER      |                                      |    |   |        |       | •     |            |

| 15       | MTVS15F4100          | Dissertation                         | НС | 0 | 2      | 20    | 22    | 40         |

|          |                      | Total Credits                        |    |   |        |       | 22    |            |

|          | Total Credits for fo | our Semesters                        |    |   |        |       | 96    |            |

**Note:** HC = Hard Core: SC= Soft Core;

# **Detailed Syllabus**

# Semester - I

| Course Code | Course Title         | Duration |    | L | T | Р | С |

|-------------|----------------------|----------|----|---|---|---|---|

| MTVS15F1100 | Advanced Mathematics | 16 Weeks | HC | 4 | 1 | 0 | 5 |

#### **Prerequisites:**

- 1. Basic knowledge of matrix mathematics and linear transformations.

- 2. Linear and parabolic partial differentiation and scalar wave equation in one space dimension.

- 3. Basics of Laplace transforms, Fourier transforms and Poisson equation by Fourier transform.

- 4. Simplex algorithm and nonlinear programming.

# **Course Objectives:**

- 1. To understand the advanced concepts in Matrix theory and calculus.

- 2. To Study the numerical, analytical and logical problem solving using transform methods.

- 3. To learn applications of Poisson and Fourier transform methods.

- 4. To understand the concept of elliptic equation.

- 5. To study the various algorithms in linear and nonlinear programming.

#### **Course Outcomes:**

On completion of this course the student will be able to:

- 1. Identify and describe different techniques in solving Engineering problems using Matrix method.

- 2. Describe the Euler equation of first and higher order degree

- 3. Apply Laplace transform to one dimensional wave.

- 4. Analyse properties of harmonic functions

- 5. Present the concepts Two Phase and Big M techniques

- 6. Explain problem solving using Lagrange's multiplier method

| Course  | POS/ | PO | PO2 | PO3 | PO4 | PO5 | PO6 | P7 | PO8 | PO9 | PO | РО | PSO1 | PSO2 | PSO3 |

|---------|------|----|-----|-----|-----|-----|-----|----|-----|-----|----|----|------|------|------|

| Code    |      | 1  |     |     |     |     |     |    |     |     | 10 | 11 |      |      |      |

|         | COs  |    |     |     |     |     |     |    |     |     |    |    |      |      |      |

| MTVS15F | CO1  | 3  | 2   | 3   | 4   |     |     |    |     | 3   |    |    | 1    | 1    | 2    |

| 1100    | CO2  | 3  | 3   | 2   | 1   |     |     |    | 2   |     |    |    |      | 2    | 1    |

|         | CO3  | 1  | 3   | 2   | 1   |     |     |    |     | 1   |    |    |      |      |      |

|         | CO4  | 2  | 3   | 1   | 2   |     |     |    |     |     |    |    |      |      |      |

|         | CO5  | 3  | 3   | 2   | 1   |     |     |    | 2   |     |    |    |      | 2    | 1    |

|         | CO6  | 3  | 3   | 2   | 1   |     |     |    | 2   |     |    |    |      | 2    | 1    |

#### **Course Contents:**

# **Unit 1:Matrix Theory, Calculus of Variations**

[16]

QR EL Decomposition – Eigen values using shifted QR algorithm- Singular Value EL Decomposition - Pseudo inverse- Least square approximations

Concept of Functional- Euler's equation – functional dependent on first and higher order derivatives – Functional on several dependent variables – Isoperimetric problems- Variation problems with moving boundaries.

#### **Unit 2:Transform Methods**

[16]

Laplace transform methods for one dimensional wave equation — Displacements in a string — Longitudinal vibration of an elastic bar — Fourier Transform methods for one dimensional heat conduction problems in infinite and semi-infinite rod.

#### **Unit 3: Elliptic Equation**

[16]

Laplace equation – Properties of harmonic functions – Fourier transforms methods for Laplace equations. Solution for Poisson equation by Fourier transforms method.

#### **Unit 4:Linear and Non Linear Programming**

[16]

Simplex Algorithm- Two Phase and Big M techniques – Duality theory- Dual Simplex method. Non Linear Programming –Constrained external problems- Lagrange's multiplier method- Kuhn-Tucker conditions and solutions. Recent trends in the related areas from journals, Conference proceedings Book chapters.

#### References:

- Richard Bronson, "Schaum's Outlines of Theory and Problems of Matrix Operations", McGraw-Hill, 1988.

- Venkataraman M. K., "Higher Engineering Mathematics", National Publications Co., 1992.

- 3. Elsgolts, L., "Differential Equations and Calculus of Variations", Mir, 1977.

- 4. Sneddon, I.N., "Elements of Partial Differential Equations", Dover Publications, 2006.

- 5. Sankara Rao, K., "Introduction to Partial Differential Equations", Prentice Hall of India, 1995.

- 6. Taha H A, "Operations Research An Introduction", McMilan Publishing co, 1982.

| Course Code | Course Title        | Duration |    | L | T | Р | С |

|-------------|---------------------|----------|----|---|---|---|---|

| MTVS15F1200 | Digital VLSI Design | 16 Weeks | HC | 4 | 0 | 1 | 5 |

### **Prerequisites:**

- 1. Working principle of MOS transistor theory and MOSFET characteristics. Static characteristics, transient response and propagation delay calculations of MOS inverters.

- 2. Basic principles of pass transistor circuits and dynamic CMOS characteristics.

- 3. Basics of volatile memory and non-volatile memory and low power CMOS logic circuits.

- 4. Knowledge on BiCMOS and BJT theory.

- 5. Concept of electrostatic discharge (ESD) and basics of latch up prevention and process variations.

#### **Course Objectives:**

- 1. To understand an overview of working principle of MOS transistor and MOS inverters.

- 2. To be acquainted with all the definitions associated with MOS inverters.

- 3. To understand dynamic logic circuits.

- 4. To get understand of semiconductor memory.

- 5. To study chip input output devices.

#### **Course Outcomes:**

On completion of this course the student will be able to:

- 1. Explain the working principle of MOS transistor and MOS inverters.

- 2. Define all the definitions associated with MOS inverters.

- 3. Analyse dynamic logic circuits.

- 4. Describe the semiconductor memory.

- 5. Explain chip input output devices.

# **Mapping of Course Outcomes with programme Outcomes**

| Cours e | POs/ | РΟ | РО | РО | РО | РО | РО | P 7 | РО | РО | PΟ | PΟ | PΟ | PS | PS | PS |

|---------|------|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|

| Code    | COs  | 1  | 2  | 3  | 4  | 5  | 6  |     | 8  | 9  | 10 | 11 | 12 | 01 | 02 | 03 |

| MTVS15F | CO1  | 3  | 2  |    | 2  |    | 1  | 1   |    |    | 2  |    | 3  |    | 3  | 2  |

| 1200    | CO2  | 3  | 3  | 3  |    |    | 1  |     |    | 2  |    |    | 2  |    | 3  | 2  |

|         | CO3  | 3  | 3  |    |    |    | 2  |     |    | 1  |    |    | 1  |    | 3  | 2  |

|         | CO4  | 3  | 3  |    |    | 2  |    |     |    |    |    |    | 1  |    | 3  | 2  |

|         | CO5  | 3  | 2  |    | 2  |    | 1  | 1   |    |    | 2  |    | 3  |    | 3  | 2  |

# **Course Contents:**

# **Unit 1:MOS Transistor, MOS Inverters**

[16]

The Metal Oxide Semiconductor (MOS) Structure, the MOS System under External Bias, Structure and Operation of MOS Transistor, MOSFET Current-Voltage Characteristics, and MOSFET Scaling and Small-Geometry Effects.

Static Characteristics: Introduction, Resistive-Load Inverter, Inverters with type MOSFET Load, CMOS Inverter.

#### **Unit 2: MOS Inverters (continued)**

[16]

Switching Characteristics and Interconnect Effects: Introduction, Delay-Time Definition, Calculation of Delay Times, and Inverter Design with Delay Constraints, Estimation of Interconnect Parasitics, Calculation of Interconnect Delay, and Switching Power Dissipation of CMOS Inverters.

Dynamic Logic Circuits: Introduction, Basic Principles of Pass Transistor Circuits, Voltage Bootstrapping, Synchronous Dynamic Circuit Techniques, Dynamic CMOS Circuit Techniques, High Performance Dynamic CMOS Circuits.

#### **Unit3: Semiconductor Memories**

[16]

Introduction, Dynamic Random Access Memory (DRAM), Static Random Access Memory (SRAM), Nonvolatile Memory, Flash Memory, Ferroelectric Random Access Memory (FRAM). Low-Power

CMOS Logic Circuits: Introduction, Overview of Power Consumption, Low-Power Design Through Voltage Scaling, Estimation and Optimization of Switching Activity, Reduction of Switched Capacitance, Adiabatic Logic Circuits.

BiCMOS Logic Circuits: Introduction, Bipolar Junction Transistor (BJT): Structure and Operation, Dynamic Behavior of BJTs, Static Behavior, Switching Delay in BiCMOS Logic Circuits, BiCMOS Applications.

# Unit 4:Chip Input and Output (I/O) Circuits

[16]

Introduction, ESD Protection, Input Circuits, Output Circuits and L (di/dt) Noise, On-Chip Clock Generation and Distribution, Latch-Up and Its Prevention.

Design for Manufacturability: Introduction, Process Variations, Basic Concepts and Definitions, Design of Experiments and Performance Modeling, Parametric Yield Estimation, Parametric Yield Maximization, Worst-Case Analysis, Performance Variability Minimization.

Recent trends in the related areas from journals, Conference proceedings Book chapters.

#### References:

- 1 Sung Mo Kang and Yosuf Leblebici, "CMOS Digital Integrated Circuits: Analysis and Design", Tata McGraw-Hill, Third Edition, 2003.

- 2. Neil Weste and K. Eshragian, "Principles of CMOS VLSI Design: A System Perspective", Second Edition, Pearson Education (Asia) Pvt. Ltd. 2000.

| Course Code | Course Title          | Duration |    | L | Т | Р | С |

|-------------|-----------------------|----------|----|---|---|---|---|

| MTVS15F1300 | Digital System Design | 16 Weeks | НС | 4 | 0 | 1 | 5 |

# **Prerequisites:**

- 1. Knowledge on Digital system design, Boolean algebraic theorems and number systems.

- 2. Basics of sequential logic and memory types.

- 3. Principles of ICs, PLDs and interfacing memory.

- 4. Basic knowledge on I/O interfacing, serial transmission and design optimization.

#### **Course Objectives:**

- 1. Present an outline in to Introduction of Digital Design and Methodology involved in Digital System Design.

- 2. Illustrate the different components and functions related to design of Combinational circuits.

- 3. Illustrate with examples the various operations and types related to Number Basics.

- 4. Illustrate the different components and methodology related to design of Sequential circuits.

- 5. Provide an understanding in to the concepts and types of memories and design of memory circuits.

- Provide an explanation in to different Digital Design Implementation Fabrics.

- 6. Provide an Understanding to concepts related to processor basics.

#### **Course Outcomes:**

- 1. Distinguish between Digital and Embedded Systems and to have an understanding of the Binary representation, elements and Design Methodology of a Digital System.

- 2. Distinguish between Combinational and Sequential Basics and to demonstrate the knowledge of Number basics.

- 3. Analyse various types of implementation fabrics.

- 4. Apply knowledge related to processor basics.

- 5. Define and describe digital design flows for system design and to recognize the trade-offs involved in different approaches.

**Mapping of Course Outcomes with programme Outcomes**

| Course | POS/ | Р | PO2 | PO3 | PO4 | PO5 | PO6 | P7 | PO8 | PO9 | РО | РО | РО | PSO1 | PSO2 | PSO3 |

|--------|------|---|-----|-----|-----|-----|-----|----|-----|-----|----|----|----|------|------|------|

| Code   |      | 0 |     |     |     |     |     |    |     |     | 10 | 11 | 12 |      |      |      |

| MTVS   | COs  | 1 |     |     |     |     |     |    |     |     |    |    |    |      |      |      |

| 15F1   | CO1  | 4 | 4   | 3   | 3   | 2   |     |    |     |     |    |    | 1  | 1    |      | 2    |

| 300    | CO2  | 1 | 4   | 3   | 3   | 2   |     |    |     |     |    |    | 2  | 1    |      | 2    |

| 300    | CO3  | 4 | 3   | 4   | 2   | 2   |     |    |     |     | 1  |    | 1  | 1    |      | 2    |

|        | CO4  | 1 | 3   | 4   |     | 2   |     |    |     |     |    |    | 1  | 1    |      | 2    |

|        | CO5  | 4 | 4   | 3   | 3   | 2   |     |    |     |     |    |    | 1  | 1    |      | 2    |

#### **Course Contents:**

# **Unit 1:Introduction and Methodology**

[16]

Digital Systems and Embedded Systems, Binary representation and Circuit Elements, Real-World Circuits, Models, Design Methodology.

Number Basics: Unsigned and Signed Integers, Fixed and Floating-point Numbers. Combinational Basics: Boolean Functions and Boolean algebra, Binary Coding, Combinational components and circuits, Verification of combinational circuits.

#### **Unit 2:Sequential Basics**

[16]

Storage elements, Counters, Sequential Data paths and Control, Clocked Synchronous Timing Methodology. Memories: Concepts, Memory Types, Error Detection and Correction.

#### **Unit 3:Implementation Fabrics**

[16]

ICs, PLDs, Packaging and Circuit Boards, Interconnection and Signal integrity. Processor Basics: Embedded Computer Organization, Instruction and Data, Interfacing with memory.

# Unit 4:I/O interfacing

[16]

I/O devices, I/O controllers, Parallel Buses, Serial Transmission, I/O software. Accelerators: Concepts, case study, Verification of accelerators.

Design Methodology: Design flow, Design optimization, Design for test.

# **References:**

1. Peter J. Ashenden, "Digital Design: An Embedded Systems Approach Using VERILOG", Elesvier, 2010.

| Course Code | Course Title            | Duration |    | L | T | Р | С |

|-------------|-------------------------|----------|----|---|---|---|---|

| MTVS15F1410 | Embedded Systems Design | 16 Weeks | SC | 4 | 1 | 0 | 5 |

## **Prerequisites:**

- 1. Concept of Embedded systems and its design optimization.

- 2. Knowledge on architecture of embedded systems and embedded microcontroller cores.

- 3. Working principle of interfacing subsystems and external systems and DSP.

- 4. Concepts of real time programming and RTOS.

# **Course Objectives:**

- 1. Understand how to design an embedded system.

- 2. To know how to partition a system to hardware and software parts efficiently.

- 3. To know Hardware/software Co-design concepts.

- 4. To understand the issues and technologies involved in designing real-time and hardware-resource constrained systems.

- 5. To be acquainted with understanding and to make decisions about general purpose computing solutions vs. specialized hardware solutions using FPGA's, CPLD.

- 6. To understand interfacing system for profiling system performance.

- 7. To be acquainted with the system architectures for optimum performance.

## **Course Outcomes:**

On completion of this course the students will be able to:

- 1. Design embedded system architectures for various applications.

- 2. Implement, Identify, formulate, and solve engineering problems.

- 3. Function on multidisciplinary teams

- 4. Implement embedded microcontroller cores.

- 5. Analyze and Apply knowledge of RTOS for various applications.

- 6. Demonstrate sub system interfacing with external system

# **Mapping of Course Outcomes with Programme Outcomes**

| Cours  | POS/ | Р | PO | PO | PO | PO | Р | PO | PO | PO | PO | PO | PO | PS | PS | PS |

|--------|------|---|----|----|----|----|---|----|----|----|----|----|----|----|----|----|

| е      | COs  | 0 | 2  | 3  | 4  | 5  | 0 | 7  | 8  | 9  | 10 | 11 | 12 | 01 | 02 | О3 |

| Code   |      | 1 |    |    |    |    | 6 |    |    |    |    |    |    |    |    |    |

| MTVS15 | CO1  | 3 | 3  | 3  |    | 2  |   |    |    | 2  | 3  |    | 3  | 2  | 3  | 2  |

| F1410  | CO2  | 3 | 3  | 3  |    | 2  |   |    |    | 2  | 3  |    | 3  | 2  | 3  | 2  |

|        | CO3  | 3 | 3  | 3  |    | 2  |   |    |    | 2  | 3  |    | 3  | 2  | 3  | 2  |

|        | CO4  | 3 | 3  | 3  |    | 2  |   |    |    | 2  | 3  |    | 3  | 2  | 3  | 2  |

|        | CO5  | 3 | 3  | 3  |    | 2  |   |    |    | 2  | 3  |    | 3  | 2  | 3  | 2  |