## SCHOOL OF ELECTRONICS AND COMMUNICATION ENGINEERING

## Organized a "Five Day FDP

On

"Hands - on Analog and Digital IC Design using Cadence Tools"

| Date                   | 7th August 2023 to 11th August 2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title                  | "Hands - on Analog and Digital IC Design using Cadence Tools"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| School                 | Electronics and Communication Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Resource<br>Person     | <ul> <li>Mr. Shivaprasad B K, Sr. FAE, Entuple Technologies Pvt. Ltd, Bengaluru</li> <li>Dr. Mamidi Nagaraja, Technical Manager, Entuple Technologies Pvt. Ltd, Bengaluru</li> <li>Dr. K M Sudarshan, Professor, REVA University, Bengaluru.</li> <li>Dr.Prashanth Joshi, Associate Professor, REVA University, Bengaluru</li> <li>Dr.Prameela Kumari, Associate Professor, REVA University, Bengaluru</li> <li>Dr. Shashank Dwivedi, Associate Professor, REVA University, Bengaluru</li> <li>Dr.A. Raganna, Associate Professor, REVA University, Bengaluru</li> <li>Prof.RaJi C, Assistant Professor, REVA University, Bengaluru</li> </ul> |

| Venue                  | Aryabhatta Seminar Hall, CV RAMAN Block, REVA University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Targeted<br>Audience   | PG Students Research Scholars, Faculty of engineering colleges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

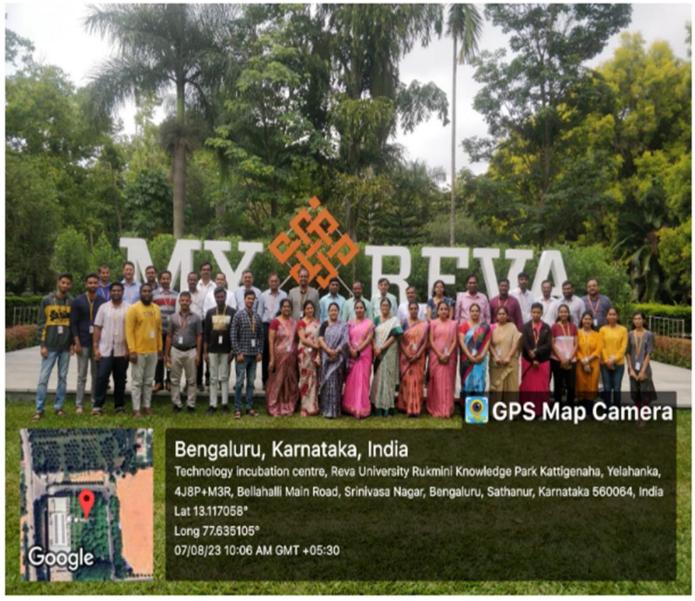

| No. of<br>Participants | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| About the event        | School of ECE organized a Five Day FDP On "Hands - on Analog and Digital IC Design using Cadence Tools" 7th August 2023 to 11th August 2023 This workshop will give exposure to Analog and Digital VLSI Design Logic to Layout, aim to introduce the most demand skills in VLSI. This FDP deals with the fundamental theory to Practical hand on training in VLSI and it is lead by industry experts, which would provide Participants to learn from the scratch to write code, design using the CMOS transistors which help them to manage their projects efficiently and make the career as a VLSI design engineer.                          |

| Description            | The following technical and hands on topics are covered by our experts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | <ul> <li>Introduction to Full Custom and Semi-Custom IC Design Flow</li> <li>Cadence Solutions for Full Custom and Semicustom IC Design</li> <li>Test bench Creation using Virtuoso Schematic Editor</li> <li>Functional Simulation using Spectre</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                   |

|                | <ul> <li>Layout Design using Virtuoso Layout Editor</li> <li>Physical Verification which includes DRC &amp; LVS</li> <li>Post Layout Simulation</li> <li>RTL Synthesis using Genus Synthesis Solution</li> <li>Physical Implementation using Innovus that includes</li> <li>Floor Planning ✓ Power Planning ✓ Placement ✓ CTS ✓ Routing</li> <li>Timing Analysis</li> <li>Power Analysis</li> <li>Parasitic Extraction</li> <li>Generation of GDSII</li> </ul>                                                                                                                                                                                                                                          |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Out Come of th | eThe primary objectives of this FDP are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Session        | <ul> <li>To acquire knowledge and skill sets in the field of latest VLSI Technology</li> <li>To improve your Technical competency by using Industry standard VLSI tools and hardware</li> <li>To stay relevant and disseminate the acquired knowledge to your student community</li> <li>To enhance career growth in core domain Give exposure to current trends and research challenges</li> <li>Event Outcomes (Course Outcome):         <ul> <li>Understand the fundamentals in the field of EDA Tools.</li> <li>Understand new areas of research and development which is VLSI tools and hardware</li> <li>Acquire the research competence in the areas like VLSI Technology</li> </ul> </li> </ul> |

| FeedBack       | PG Students and Faculties have expressed their overwhelming feedback response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Analysis       | with a rating as a good. They have felt that the hands on session was very educative and informative. They have also expressed their concent for attending many more such FDPs on this domain in future.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Coordinators   | Dr. Venkateshappa, Professor, School of ECE.  Dr.Seshikala, Professor, School of ECE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Director       | Dr. K.M. Sudarshan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |